Shasta VISC Architecture Allows Single Thread Execution Across Virtual Cores - Aims for 3-4x IPC Improvement

If you're keeping tabs on the rumors in technology land, you will most likely have heard about the "inverse hyper-threading" technologies that are (allegedly) present in Skylake and future AMD processors. Soft Machines' recent disclosure at the Linley Processor Conference may help understand what this technology is all about.

To keep things very simple, consider Hyper-Threading. This technology allows the operating system to increase the number of independent instructions operate at the same time. Instead of one instruction executed on a phyiscal core, you can have two. This greatly improves the parallel computing performance, as you of course know from benchmarks like Cinebench or Wprime. Inverse or Reverse Hyper-threading implies that instead of using one core to process two threads, you would use two cores to execute one thread. Soft Machines' VISC architecture is a design that does exactly this. By using multiple virtual cores, it spreads instructions across the available virtual cores to complete the workload faster. This technology is said to increase the IPC (instructions per cycle) by a factor of up to 4x.

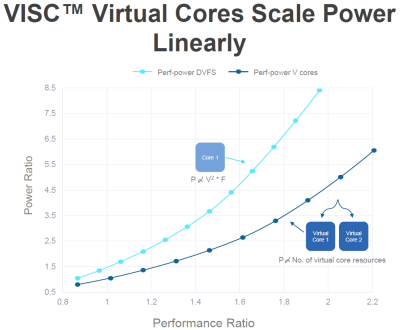

The key points of the Soft Machine VISC architecture are that the operating frequency has been increased from 500 MHz to 2 GHz from the early prototype to the current engineering samples. This is important because it addresses the problem of increased power consumption as performance increases. With traditional designs, to scale the frequency (and thus performance) you need an exponential increase in voltage. In addition, Soft Machines indicates to have no ambition of competing in the processor market, but rather licensing the technology. That means AMD, Intel, Qualcomm, and other manufacturers can integrate the technology in future products. Thirdly, as we mentioned before the IPC improvement could drastically impact the way we experience computing. Last but not least, Soft Machines indicates that the VISC architecture can support up to two additional ISA (instruction set architecture). For example: x86 and ARM.

Thanks to the power efficient performance scaling, Soft Machines says to be able to supply for markets ranging from low-power mobile to high-performance server. If you're interested in learning more, the presentation at Linley Processor Conference 2015 is available on YouTube and is a highly recommended watch

Please log in or register to comment.